DIENTU.VN & DIENTUVIETNAM.VN Tập trung nghiên cứu và phát triển Semiconductor, từ thiết kế vi mạch đến ứng dụng thực tế.

Chuyên sâu Lập trình FPGA, triển khai thuật toán phần cứng tốc độ cao cho hệ thống nhúng và AI.

Giải pháp Camera tích hợp FPGA

Giải pháp camera tích hợp FPGA cho phép xử lý hình ảnh trực tiếp ở mức phần cứng, đáp ứng yêu cầu độ trễ thấp, tốc độ cao và độ ổn định cao so với xử lý bằng CPU/GPU truyền thống.

Hệ thống phù hợp cho các ứng dụng AI Vision, giám sát thông minh, công nghiệp, giao thông, với khả năng tùy biến pipeline xử lý ảnh, nén video và tăng tốc thuật toán theo yêu cầu thực tế.

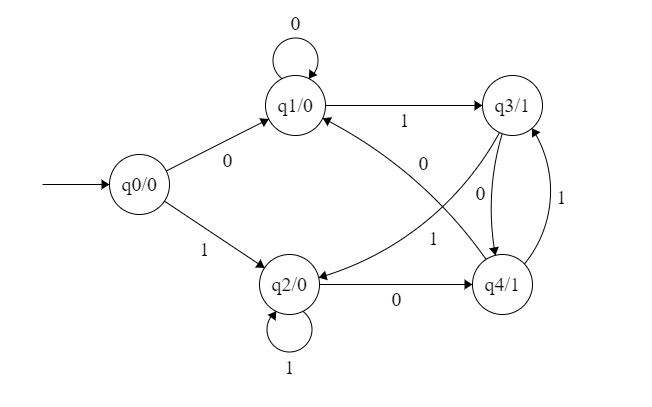

Trong thiết kế FPGA và vi mạch số, FSM (Finite State Machine – Máy trạng thái hữu hạn) là một khái niệm cốt lõi, đặc biệt khi xây dựng bộ điều khiển, giao thức truyền thông, xử lý tuần tự trên Verilog/VHDL.

Bài viết này sẽ giúp bạn:

-

Hiểu rõ FSM là gì

-

Phân biệt Mealy FSM và Moore FSM

-

Biết khi nào nên dùng Mealy hay Moore trong thiết kế FPGA (PYNQ-Z2, Zynq-7000…)

FSM là gì? (Finite State Machine)

FSM – Máy trạng thái hữu hạn là một mô hình điều khiển gồm:

-

Một tập trạng thái hữu hạn

-

Trạng thái hiện tại

-

Tín hiệu vào (input)

-

Tín hiệu ra (output)

-

Luật chuyển trạng thái

FSM quyết định đầu ra và trạng thái tiếp theo dựa trên:

-

Trạng thái hiện tại

-

Và/hoặc tín hiệu vào

Ứng dụng FSM trong FPGA

-

Bộ điều khiển UART, SPI, I2C

-

Giao thức AXI-lite

-

Bộ điều khiển LED, nút nhấn

-

State machine cho CPU, DMA

-

Xử lý chuỗi, giải mã giao thức

Hai dạng FSM phổ biến

Trong thiết kế số, FSM có 2 dạng chính:

| Dạng FSM | Đặc điểm |

|---|---|

| Moore FSM | Output phụ thuộc chỉ vào trạng thái |

| Mealy FSM | Output phụ thuộc trạng thái + input |

Moore FSM là gì?

Đặc điểm

-

Output chỉ thay đổi khi trạng thái thay đổi

-

Output ổn định, đồng bộ theo clock

-

Dễ thiết kế, dễ debug

Mô hình hoạt động

Công thức:

Ưu điểm

✅ Output ổn định, ít glitch

✅ Phù hợp hệ thống clock cao

✅ Dễ tổng hợp trên FPGA

Nhược điểm

❌ Phản ứng chậm hơn (thường trễ 1 chu kỳ clock)

❌ Có thể cần nhiều trạng thái hơn

Mealy FSM là gì?

Đặc điểm

-

Output phụ thuộc trạng thái hiện tại và input

-

Output có thể thay đổi ngay khi input thay đổi

-

Phản hồi nhanh

Mô hình hoạt động

Công thức:

Ưu điểm

✅ Phản ứng nhanh, không cần đợi clock

✅ Ít trạng thái hơn Moore FSM

✅ Tiết kiệm tài nguyên logic

Nhược điểm

❌ Dễ xuất hiện glitch nếu input nhiễu

❌ Khó debug hơn

❌ Cần xử lý timing cẩn thận

So sánh Mealy FSM và Moore FSM

| Tiêu chí | Moore FSM | Mealy FSM |

|---|---|---|

| Output phụ thuộc | Trạng thái | Trạng thái + Input |

| Thời điểm thay đổi output | Theo clock | Ngay khi input đổi |

| Độ ổn định | ⭐⭐⭐⭐ | ⭐⭐ |

| Độ phản hồi | ⭐⭐ | ⭐⭐⭐⭐ |

| Số trạng thái | Nhiều hơn | Ít hơn |

| Độ phức tạp | Dễ | Khó hơn |

| Nguy cơ glitch | Thấp | Cao hơn |

Nên dùng Mealy hay Moore trong FPGA?

Nên dùng Moore FSM khi:

-

Thiết kế cho người mới học FPGA

-

Hệ thống yêu cầu output ổn định

-

Điều khiển LED, LCD, FSM điều khiển tổng quát

-

Thiết kế trên PYNQ-Z2 / Zynq-7000

Nên dùng Mealy FSM khi:

-

Cần phản hồi nhanh

-

Giao thức truyền thông (UART RX, SPI)

-

Tối ưu số trạng thái

-

Có kinh nghiệm xử lý timing & glitch

Khuyến nghị thực tế:

Bắt đầu bằng Moore FSM, chỉ dùng Mealy FSM khi thật sự cần tốc độ.

FSM trong Verilog – lưu ý quan trọng

Dù là Mealy hay Moore, FSM chuẩn FPGA nên có 3 khối rõ ràng:

-

State register (always @(posedge clk))

-

Next state logic

-

Output logic

Việc tách rõ 3 khối giúp:

-

Dễ debug

-

Dễ mở rộng

-

Tránh lỗi timing