DIENTU.VN & DIENTUVIETNAM.VN Tập trung nghiên cứu và phát triển Semiconductor, từ thiết kế vi mạch đến ứng dụng thực tế.

Chuyên sâu Lập trình FPGA, triển khai thuật toán phần cứng tốc độ cao cho hệ thống nhúng và AI.

Giải pháp Camera tích hợp FPGA

Giải pháp camera tích hợp FPGA cho phép xử lý hình ảnh trực tiếp ở mức phần cứng, đáp ứng yêu cầu độ trễ thấp, tốc độ cao và độ ổn định cao so với xử lý bằng CPU/GPU truyền thống.

Hệ thống phù hợp cho các ứng dụng AI Vision, giám sát thông minh, công nghiệp, giao thông, với khả năng tùy biến pipeline xử lý ảnh, nén video và tăng tốc thuật toán theo yêu cầu thực tế.

Trong thiết kế số với VHDL, FSM Moore là dạng được khuyến nghị nhất cho FPGA vì:

-

Output ổn định, chỉ phụ thuộc trạng thái

-

Dễ mô phỏng, dễ debug

-

Dễ đạt timing khi synthesize

Bài viết này hướng dẫn bạn cách mô tả FSM Moore đúng chuẩn, kèm ví dụ VHDL hoàn chỉnh và các lưu ý quan trọng.

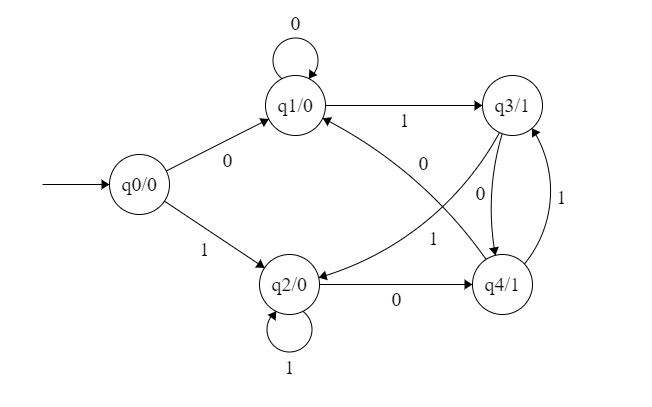

1. Ôn nhanh: FSM Moore là gì?

FSM Moore là máy trạng thái mà:

-

Output = f(State)

-

Không phụ thuộc trực tiếp vào input

👉 Output chỉ thay đổi khi state thay đổi (tức là theo clock).

Minh họa FSM Moore

2. Cấu trúc chuẩn của FSM Moore trong VHDL

FSM Moore chuẩn FPGA luôn gồm 3 khối tách biệt:

-

State register (mạch tuần tự)

-

Next-state logic (mạch tổ hợp)

-

Output logic (mạch tổ hợp, phụ thuộc state)

👉 Đây là best practice, rất nên tuân theo.

3. Ví dụ FSM Moore đơn giản (bật/tắt LED)

Yêu cầu

-

Nhấn nút

btn:-

Từ

IDLE→ON -

Từ

ON→IDLE

-

-

LED sáng khi ở trạng thái

ON

4. Khai báo trạng thái (ENUM – rất khuyến nghị)

✅ Code rõ ràng

✅ Tool tự tối ưu encoding

✅ Tránh lỗi nhầm bit

5. Khối 1 – State Register (FSM + reset)

📌 Lưu ý:

-

Reset đồng bộ (khuyến nghị)

-

Chỉ cập nhật state, không xử lý logic khác

6. Khối 2 – Next State Logic (tổ hợp)

📌 Rất quan trọng:

-

Luôn gán giá trị mặc định

-

Tránh latch ngoài ý muốn

7. Khối 3 – Output Logic (Moore FSM)

👉 Output chỉ phụ thuộc state → đúng bản chất Moore FSM.

8. Ghép lại: FSM Moore hoàn chỉnh bằng VHDL

9. Những lỗi thường gặp khi mô tả FSM Moore

❌ Output phụ thuộc input → thành Mealy FSM

❌ Không gán next_state mặc định → tạo latch

❌ Gộp cả FSM + output + logic vào 1 process → khó debug

❌ Reset không đưa FSM về state xác định

10. Checklist FSM Moore chuẩn VHDL

-

State dùng

enum -

Có state reset rõ ràng

-

3 process tách biệt

-

Output chỉ phụ thuộc

state -

Không latch

-

Mô phỏng trước khi synthesize

11. Khi nào nên dùng FSM Moore?

-

Điều khiển LED, relay, LCD

-

FSM tổng quát trong FPGA

-

Người mới học VHDL

-

Hệ thống cần output ổn định

👉 90% FSM trong FPGA có thể dùng Moore FSM.