DIENTU.VN & DIENTUVIETNAM.VN Tập trung nghiên cứu và phát triển Semiconductor, từ thiết kế vi mạch đến ứng dụng thực tế.

Chuyên sâu Lập trình FPGA, triển khai thuật toán phần cứng tốc độ cao cho hệ thống nhúng và AI.

Giải pháp Camera tích hợp FPGA

Giải pháp camera tích hợp FPGA cho phép xử lý hình ảnh trực tiếp ở mức phần cứng, đáp ứng yêu cầu độ trễ thấp, tốc độ cao và độ ổn định cao so với xử lý bằng CPU/GPU truyền thống.

Hệ thống phù hợp cho các ứng dụng AI Vision, giám sát thông minh, công nghiệp, giao thông, với khả năng tùy biến pipeline xử lý ảnh, nén video và tăng tốc thuật toán theo yêu cầu thực tế.

Khi học và làm việc với FPGA / thiết kế số, hai ngôn ngữ HDL phổ biến nhất là Verilog và VHDL.

Việc chọn ngôn ngữ nào ảnh hưởng trực tiếp đến:

-

Tốc độ học

-

Cách tư duy thiết kế

-

Hiệu quả làm dự án FPGA thực tế

Bài viết này sẽ giúp bạn hiểu rõ sự khác nhau, ưu – nhược điểm và nên chọn Verilog hay VHDL trong từng trường hợp.

Tổng quan Verilog và VHDL

| Tiêu chí | Verilog | VHDL |

|---|---|---|

| Năm ra đời | 1984 | 1987 |

| Phong cách | Giống C | Giống Ada |

| Độ phổ biến | Rất cao | Cao (nhất là châu Âu) |

| Ứng dụng | FPGA & ASIC | FPGA & ASIC |

1. Verilog là gì?

Đặc điểm chính

-

Cú pháp ngắn gọn, dễ đọc

-

Gần với ngôn ngữ lập trình C

-

Rất phổ biến trong FPGA thương mại & startup

Ví dụ Verilog (counter)

Ưu điểm của Verilog

✅ Dễ học, dễ viết

✅ Code ngắn, ít dòng

✅ Phù hợp sinh viên & người mới học FPGA

✅ Cộng đồng lớn, nhiều ví dụ

Nhược điểm của Verilog

❌ Kiểu dữ liệu đơn giản → dễ viết sai

❌ Ít ràng buộc → bug khó phát hiện sớm

❌ Dự án lớn dễ khó bảo trì nếu code không chặt

2. VHDL là gì?

Đặc điểm chính

-

Cú pháp chặt chẽ, tường minh

-

Kiểu dữ liệu mạnh, kiểm tra lỗi sớm

-

Phổ biến trong hệ thống công nghiệp, hàng không, quốc phòng

Ví dụ VHDL (counter)

Ưu điểm của VHDL

✅ Kiểm soát lỗi tốt

✅ Rõ ràng, dễ đọc logic với dự án lớn

✅ Phù hợp tiêu chuẩn công nghiệp

✅ An toàn hơn cho hệ thống quan trọng

Nhược điểm của VHDL

❌ Cú pháp dài, nhiều dòng

❌ Học chậm hơn Verilog

❌ Ít “linh hoạt” khi thử nghiệm nhanh

3. So sánh chi tiết Verilog vs VHDL

3.1 Cú pháp & độ dễ học

| Tiêu chí | Verilog | VHDL |

|---|---|---|

| Độ ngắn gọn | ⭐⭐⭐⭐ | ⭐⭐ |

| Dễ học ban đầu | ⭐⭐⭐⭐ | ⭐⭐ |

| Độ tường minh | ⭐⭐ | ⭐⭐⭐⭐ |

👉 Verilog phù hợp học nhanh

👉 VHDL phù hợp học kỹ, bài bản

3.2 Kiểu dữ liệu & độ an toàn

| Tiêu chí | Verilog | VHDL |

|---|---|---|

| Kiểu dữ liệu | Đơn giản | Rất mạnh |

| Bắt lỗi sớm | ❌ | ✅ |

| Nguy cơ bug ngầm | Cao hơn | Thấp hơn |

👉 VHDL giúp bắt lỗi ngay khi compile

3.3 Quy mô dự án

| Quy mô | Nên dùng |

|---|---|

| Bài học, đồ án sinh viên | Verilog |

| Prototype nhanh | Verilog |

| Dự án công nghiệp lớn | VHDL |

| Hệ thống an toàn cao | VHDL |

4. Hiệu năng & tài nguyên FPGA – có khác nhau không?

👉 Câu trả lời: KHÔNG ĐÁNG KỂ

-

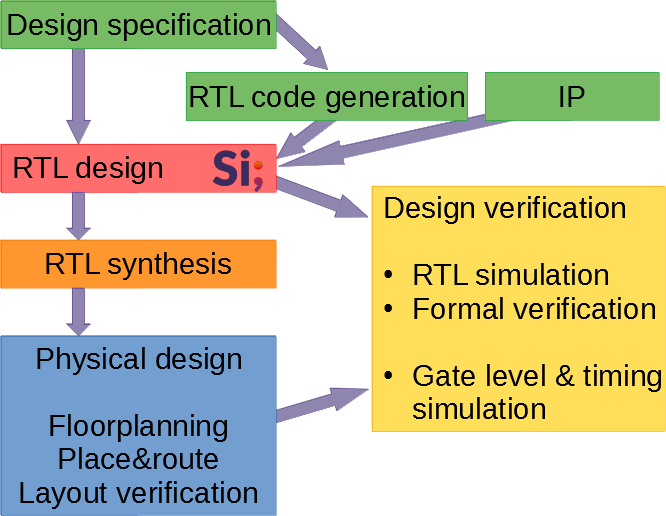

Verilog và VHDL đều là RTL HDL

-

Synthesis tool sẽ tạo phần cứng giống nhau nếu:

-

Thuật toán giống

-

Kiến trúc giống

-

⚠️ Hiệu năng phụ thuộc cách viết, không phải ngôn ngữ.

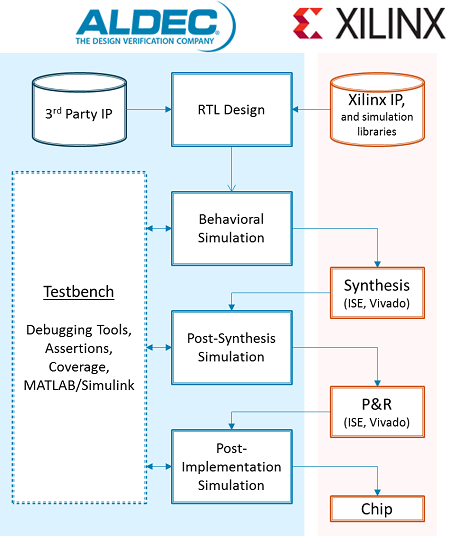

5. Tool FPGA hỗ trợ ra sao?

-

Vivado, Quartus, Libero: hỗ trợ cả Verilog & VHDL

-

Verilog thường được:

-

Ví dụ nhiều hơn

-

IP core mẫu dùng nhiều hơn

-

6. Nên chọn Verilog hay VHDL?

👉 Chọn Verilog nếu bạn:

-

Mới học FPGA

-

Làm nhanh đồ án, prototype

-

Đọc tài liệu/opensource nhiều

-

Muốn code gọn

👉 Chọn VHDL nếu bạn:

-

Làm dự án lớn, dài hạn

-

Yêu cầu độ ổn định cao

-

Làm trong môi trường công nghiệp

-

Muốn kiểm soát lỗi chặt chẽ

👉 Thực tế: rất nhiều kỹ sư giỏi biết cả hai.

7. Lời khuyên thực tế cho người mới học FPGA

🔹 Bắt đầu bằng Verilog → hiểu bản chất mạch số → học thêm VHDL sau

Vì:

-

Tư duy RTL là quan trọng nhất

-

Đổi ngôn ngữ chỉ là đổi cú pháp