DIENTU.VN & DIENTUVIETNAM.VN Tập trung nghiên cứu và phát triển Semiconductor, từ thiết kế vi mạch đến ứng dụng thực tế.

Chuyên sâu Lập trình FPGA, triển khai thuật toán phần cứng tốc độ cao cho hệ thống nhúng và AI.

Giải pháp Camera tích hợp FPGA

Giải pháp camera tích hợp FPGA cho phép xử lý hình ảnh trực tiếp ở mức phần cứng, đáp ứng yêu cầu độ trễ thấp, tốc độ cao và độ ổn định cao so với xử lý bằng CPU/GPU truyền thống.

Hệ thống phù hợp cho các ứng dụng AI Vision, giám sát thông minh, công nghiệp, giao thông, với khả năng tùy biến pipeline xử lý ảnh, nén video và tăng tốc thuật toán theo yêu cầu thực tế.

Đối với sinh viên điện tử, kỹ sư nhúng hoặc người mới học FPGA, việc đưa một mạch số từ ý tưởng → HDL → chạy thật trên board là kỹ năng bắt buộc.

Bài viết này trình bày quy trình chuẩn, dễ hiểu và đúng thực tế, áp dụng cho hầu hết FPGA hiện nay (Xilinx/Intel).

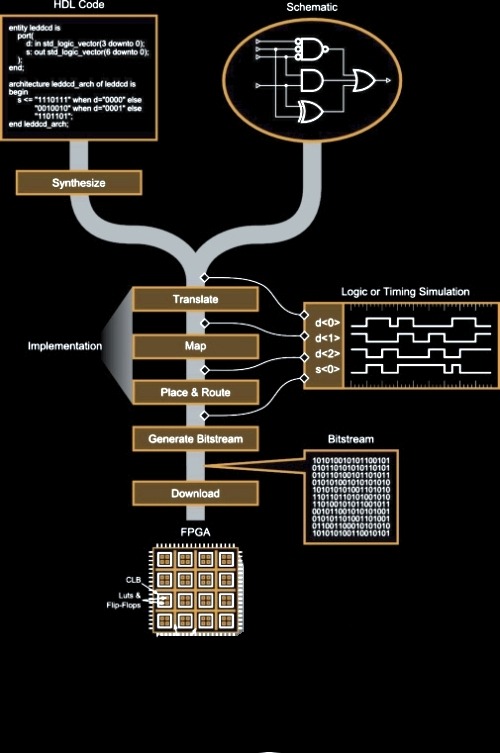

Tổng quan quy trình triển khai FPGA

Luồng chuẩn gồm 8 bước chính:

-

Xác định yêu cầu thiết kế

-

Mô tả mạch bằng HDL (Verilog/VHDL)

-

Mô phỏng (Simulation)

-

Tạo project FPGA

-

Tổng hợp (Synthesis)

-

Gán chân & constraint

-

Implement & tạo bitstream

-

Nạp FPGA và kiểm tra thực tế

1. Xác định yêu cầu thiết kế (Specification)

Trước khi viết HDL, cần trả lời rõ:

-

Mạch làm chức năng gì?

-

Tần số clock bao nhiêu?

-

Input/Output gồm những tín hiệu nào?

-

Có dùng FSM, counter, bộ nhớ không?

-

Chạy độc lập hay giao tiếp với CPU/ngoại vi?

👉 Sai từ bước này → sửa rất tốn thời gian về sau.

2. Mô tả mạch bằng HDL (Verilog/VHDL)

Viết code RTL rõ ràng

-

Phân biệt logic tổ hợp và logic tuần tự

-

FSM viết rõ state register / next state / output

-

Reset rõ ràng (ưu tiên reset đồng bộ)

Ví dụ cấu trúc chuẩn:

-

Module top

-

Các module con (counter, FSM, datapath…)

👉 Mục tiêu: code đúng chức năng + dễ synthesize

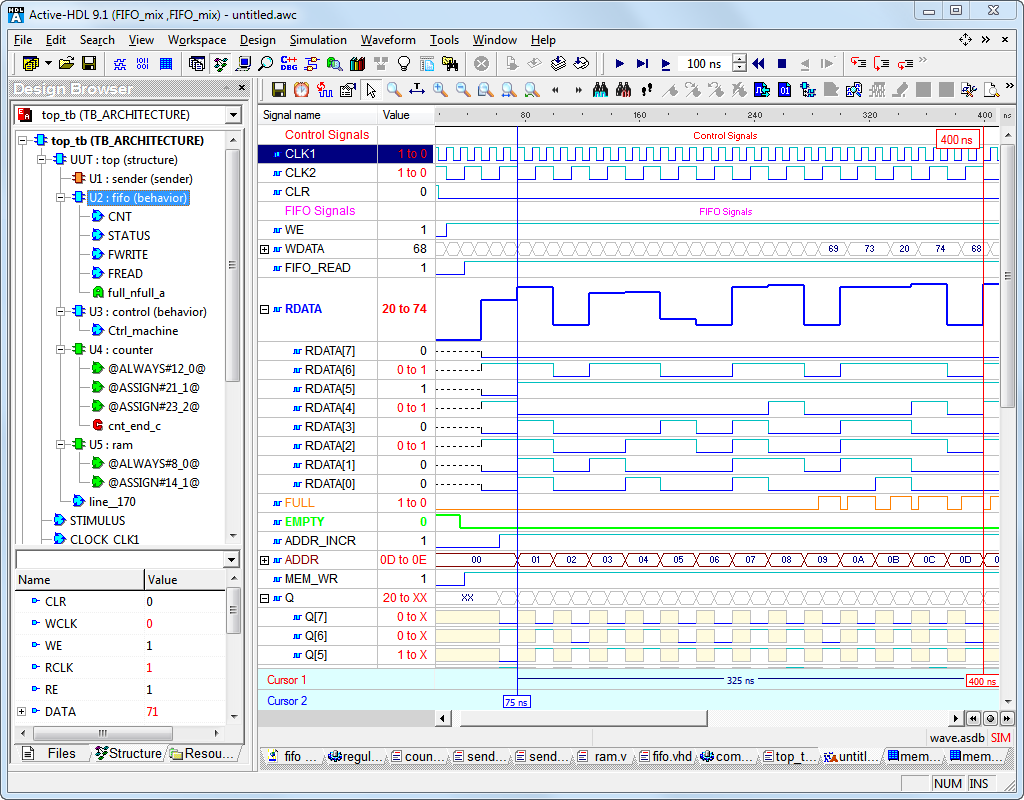

3. Mô phỏng (Simulation) – BẮT BUỘC

Tại sao phải mô phỏng?

-

Kiểm tra logic trước khi lên FPGA

-

Bắt lỗi FSM, reset, counter

-

Tiết kiệm rất nhiều thời gian debug

Cần có:

-

RTL code

-

Testbench (tạo clock, reset, stimulus)

-

Xem waveform

👉 Không mô phỏng = debug mù trên phần cứng

4. Tạo project FPGA trong tool

Dùng tool tương ứng với hãng FPGA:

-

Chọn đúng chip/board

-

Add file HDL

-

Add file simulation

📌 Lưu ý:

-

Sai chip → synthesize vẫn chạy nhưng không nạp được

-

Chọn đúng tốc độ (speed grade) nếu có

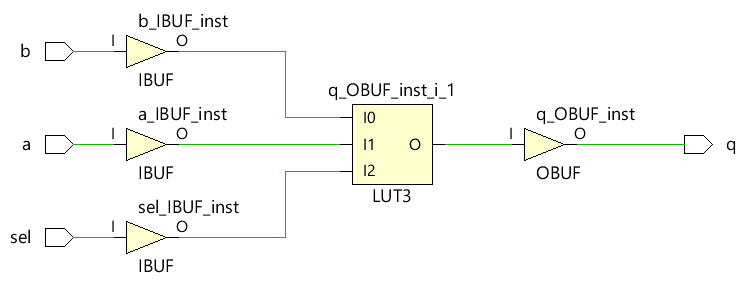

5. Tổng hợp (Synthesis)

Synthesis làm gì?

-

Biến HDL → LUT, FF, BRAM, DSP

-

Tạo netlist logic

Cần kiểm tra:

-

Số LUT / FF / BRAM / DSP

-

Có warning latch không?

-

FSM có được nhận diện đúng không?

👉 Đây là bước đầu phát hiện thiết kế có quá nặng không.

6. Gán chân & constraint (XDC / SDC)

Gán chân (Pin assignment)

-

LED, button, switch

-

UART, SPI, I2C

-

Clock đầu vào

Constraint clock (RẤT QUAN TRỌNG)

-

Khai báo tần số clock thực tế

-

Thiếu constraint → timing report không tin được

📌 Đây là bước liên kết HDL với phần cứng thật.

7. Implement & tạo bitstream

Implementation gồm:

-

Place (đặt logic)

-

Route (định tuyến)

Kiểm tra:

-

Timing summary

-

Setup slack ≥ 0

-

Hold slack ≥ 0

-

-

Critical path ở đâu?

👉 Nếu timing fail → phải quay lại tối ưu code.

8. Nạp FPGA & kiểm tra thực tế

Nạp bitstream

-

Qua JTAG / USB

-

FPGA chạy mạch thật

Kiểm tra:

-

LED có đúng không?

-

FSM có chạy đúng trạng thái?

-

Clock có đúng tần số?

-

Có lỗi ngẫu nhiên không?

👉 Nếu mô phỏng đúng mà chạy sai → thường do:

-

Reset

-

Constraint clock

-

Input không đồng bộ

9. Vòng lặp debug (thực tế luôn có)

Thiết kế FPGA không bao giờ xong ngay lần đầu:

👉 Debug tốt = tiết kiệm 70% thời gian dự án.

10. Checklist nhanh cho người mới học FPGA

-

Yêu cầu thiết kế rõ ràng

-

Code HDL đúng chuẩn RTL

-

Có testbench & waveform

-

Không có latch

-

Clock & reset rõ ràng

-

Constraint đúng

-

Timing pass

-

Test trên board thật

Kết luận

Triển khai mạch số lên FPGA không chỉ là viết HDL, mà là một quy trình kỹ thuật hoàn chỉnh.

Người làm FPGA giỏi là người:

-

Hiểu từng bước

-

Biết lỗi thường nằm ở đâu

-

Luôn mô phỏng & đọc report