DIENTU.VN & DIENTUVIETNAM.VN Tập trung nghiên cứu và phát triển Semiconductor, từ thiết kế vi mạch đến ứng dụng thực tế.

Chuyên sâu Lập trình FPGA, triển khai thuật toán phần cứng tốc độ cao cho hệ thống nhúng và AI.

Giải pháp Camera tích hợp FPGA

Giải pháp camera tích hợp FPGA cho phép xử lý hình ảnh trực tiếp ở mức phần cứng, đáp ứng yêu cầu độ trễ thấp, tốc độ cao và độ ổn định cao so với xử lý bằng CPU/GPU truyền thống.

Hệ thống phù hợp cho các ứng dụng AI Vision, giám sát thông minh, công nghiệp, giao thông, với khả năng tùy biến pipeline xử lý ảnh, nén video và tăng tốc thuật toán theo yêu cầu thực tế.

Timing violation là lỗi rất thường gặp khi thiết kế số bằng HDL (Verilog/VHDL), đặc biệt trên FPGA. Nếu không xử lý đúng, mạch có thể:

-

Chạy không ổn định

-

Sai dữ liệu ngẫu nhiên

-

Chỉ lỗi khi lên board thật (mô phỏng vẫn đúng)

Bài viết này giúp bạn hiểu bản chất, phân loại lỗi timing và cách khắc phục hiệu quả, thực tế.

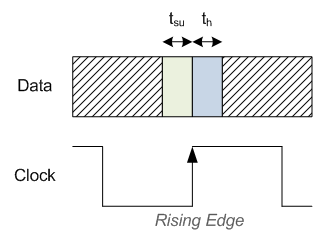

1. Timing violation là gì?

Timing violation xảy ra khi dữ liệu không đáp ứng yêu cầu thời gian của flip-flop hoặc logic, gồm:

-

Setup violation: dữ liệu đến quá trễ

-

Hold violation: dữ liệu đến quá sớm

Nói ngắn gọn: logic chạy chậm hơn (hoặc nhanh hơn) so với yêu cầu clock.

2. Hai loại timing violation cơ bản

2.1 Setup Time Violation (phổ biến nhất)

Xảy ra khi:

-

Đường dữ liệu quá dài

-

Clock quá nhanh

-

Logic giữa 2 FF quá phức tạp

👉 Dữ liệu chưa kịp ổn định trước cạnh clock.

2.2 Hold Time Violation (nguy hiểm nhưng khó thấy)

Xảy ra khi:

-

Đường dữ liệu quá ngắn

-

Clock skew

-

Reset/enable không đồng bộ

👉 Dữ liệu thay đổi quá sớm ngay sau cạnh clock.

3. Dấu hiệu nhận biết timing violation

-

Vivado/Quartus báo:

-

❌ Setup Slack < 0

-

❌ Hold Slack < 0

-

-

Mạch:

-

Chạy lúc được lúc không

-

Sai ngẫu nhiên

-

Chỉ lỗi ở tần số cao

-

4. Quy trình xử lý timing violation (CHUẨN)

Bước 1: Đọc báo cáo timing (rất quan trọng)

Xem các mục:

-

Worst Negative Slack (WNS)

-

Total Negative Slack (TNS)

-

Critical Path

👉 Đừng sửa code trước khi biết đường nào chậm nhất.

Bước 2: Xác định loại violation

-

Slack âm ở setup → xử lý logic/chia pipeline

-

Slack âm ở hold → thêm delay/buffer (tool thường tự xử)

5. Cách xử lý Setup Violation (80% trường hợp)

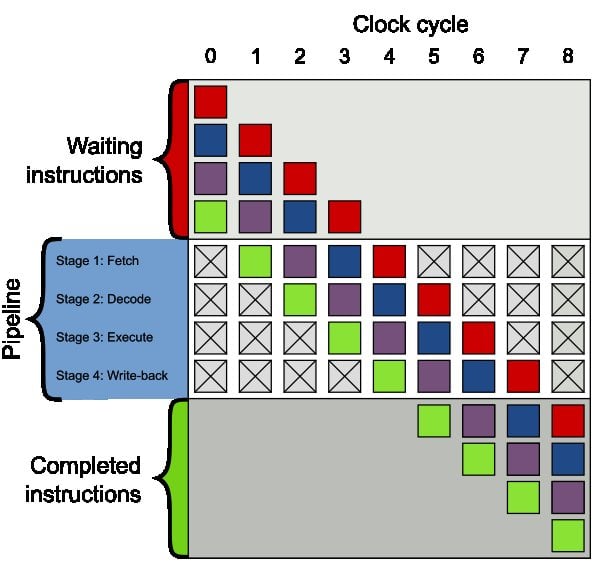

5.1 Giảm độ phức tạp logic (tách pipeline)

Sai (logic dài trong 1 chu kỳ):

Đúng (pipeline):

✅ Giảm delay mỗi chu kỳ

✅ Dễ đạt Fmax cao hơn

5.2 Giảm tần số clock (khi không cần quá nhanh)

-

Từ 200 MHz → 100 MHz

-

Hoặc dùng clock enable thay vì tăng clock

5.3 Dùng tài nguyên chuyên dụng (DSP/BRAM)

-

Phép nhân/cộng lớn → dùng DSP

-

Bộ nhớ → BRAM

👉 Tránh để tool suy ra LUT cho các phép nặng.

5.4 Tối ưu FSM

-

Giảm số trạng thái

-

Tránh logic IF–ELSE lồng quá sâu trong 1 state

6. Cách xử lý Hold Violation

6.1 Đừng “sửa tay” vội

👉 Với FPGA hiện đại:

-

Hold violation thường do routing

-

Tool tự fix bằng delay buffer

6.2 Kiểm tra reset & enable

-

Reset async nhả không đồng bộ

-

Enable không đồng bộ clock

👉 Dùng:

-

Reset đồng bộ

-

Enable đồng bộ theo clock

7. Những lỗi coding gây timing violation (rất hay gặp)

❌ Tạo clock bằng logic

✅ Dùng clock enable

❌ Bit-width quá lớn

✅ Vừa đủ

8. Timing constraint – đừng bỏ qua!

Nếu constraint sai hoặc thiếu, tool không thể tối ưu đúng.

Tối thiểu cần có:

-

Clock constraint (

create_clock) -

Input/Output delay (nâng cao)

👉 Thiếu constraint = timing report không đáng tin.

9. Checklist nhanh xử lý timing violation

-

Đọc Critical Path

-

Xác định setup hay hold

-

Thêm pipeline nếu logic dài

-

Giảm clock nếu có thể

-

Dùng DSP / BRAM

-

Không tạo clock mới bằng logic

-

Reset & enable đồng bộ

-

Constraint đúng và đủ

10. Kết luận (rất quan trọng)

Timing violation không phải “tool yếu”, mà thường do cách thiết kế.

Thiết kế số tốt là:

-

Chia nhỏ logic

-

Đồng bộ rõ ràng

-

Cho tool cơ hội tối ưu