DIENTU.VN & DIENTUVIETNAM.VN Tập trung nghiên cứu và phát triển Semiconductor, từ thiết kế vi mạch đến ứng dụng thực tế.

Chuyên sâu Lập trình FPGA, triển khai thuật toán phần cứng tốc độ cao cho hệ thống nhúng và AI.

Giải pháp Camera tích hợp FPGA

Giải pháp camera tích hợp FPGA cho phép xử lý hình ảnh trực tiếp ở mức phần cứng, đáp ứng yêu cầu độ trễ thấp, tốc độ cao và độ ổn định cao so với xử lý bằng CPU/GPU truyền thống.

Hệ thống phù hợp cho các ứng dụng AI Vision, giám sát thông minh, công nghiệp, giao thông, với khả năng tùy biến pipeline xử lý ảnh, nén video và tăng tốc thuật toán theo yêu cầu thực tế.

Trong thiết kế FPGA bằng VHDL, reset là phần rất quan trọng vì nó quyết định:

-

Trạng thái khởi động của hệ thống

-

Độ ổn định khi chạy thực tế

-

Khả năng synthesize và đạt timing

Bài viết này sẽ giúp bạn:

-

Hiểu rõ reset đồng bộ và reset không đồng bộ

-

Biết cách viết VHDL đúng chuẩn

-

Biết khi nào nên dùng loại nào trong FPGA

1. Reset là gì trong mạch số?

Reset là tín hiệu đưa mạch về trạng thái ban đầu xác định:

-

Thanh ghi = 0

-

FSM về state IDLE

-

Counter về giá trị ban đầu

👉 Trong FPGA, reset thường dùng cho:

-

Flip-Flop

-

Register

-

FSM

-

Datapath

2. Reset không đồng bộ (Asynchronous Reset)

Khái niệm

Reset không đồng bộ là reset không phụ thuộc clock:

-

Reset có hiệu lực ngay lập tức

-

Không cần đợi cạnh clock

Đặc điểm

-

Reset tác động tức thì

-

Hay dùng cho power-up reset

-

Dễ gây lỗi timing nếu nhả reset không đúng

Sơ đồ nguyên lý

Cách viết reset không đồng bộ trong VHDL

📌 Lưu ý:

-

rst_nthường là active-low -

Reset được kiểm tra trước clock

-

Phải khai báo reset trong sensitivity list

Ưu & nhược điểm

✅ Ưu điểm:

-

Reset nhanh, tức thì

-

Phù hợp reset khi bật nguồn

❌ Nhược điểm:

-

Dễ gây metastability khi nhả reset

-

Khó timing closure hơn

-

Không phù hợp hệ thống clock phức tạp

3. Reset đồng bộ (Synchronous Reset)

Khái niệm

Reset đồng bộ chỉ có hiệu lực tại cạnh clock:

-

Reset chỉ được lấy mẫu khi có clock

-

Giống một tín hiệu điều khiển bình thường

Đặc điểm

-

Reset ổn định, an toàn timing

-

Dễ kiểm soát trong hệ thống lớn

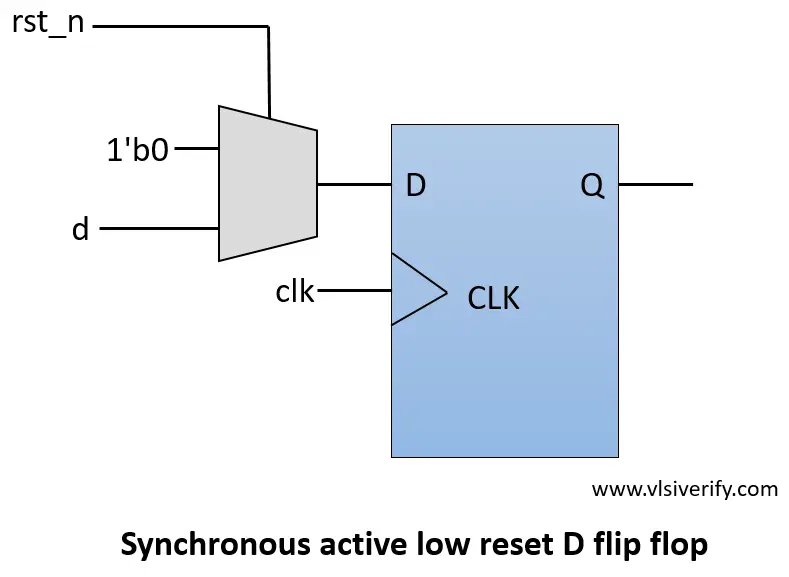

Sơ đồ nguyên lý

Cách viết reset đồng bộ trong VHDL

📌 Lưu ý:

-

Reset không nằm trong sensitivity list

-

Reset được kiểm tra bên trong clock

Ưu & nhược điểm

✅ Ưu điểm:

-

Dễ đạt timing

-

Không lo glitch/reset sai pha

-

Khuyến nghị cho FSM & datapath

❌ Nhược điểm:

-

Reset chậm hơn (đợi clock)

-

Không dùng được khi clock chưa chạy

4. So sánh reset đồng bộ và không đồng bộ

| Tiêu chí | Reset không đồng bộ | Reset đồng bộ |

|---|---|---|

| Phụ thuộc clock | ❌ | ✅ |

| Thời điểm tác động | Ngay lập tức | Theo clock |

| Độ an toàn timing | ⭐⭐ | ⭐⭐⭐⭐ |

| Nguy cơ metastability | Cao | Thấp |

| Dễ synthesize | Trung bình | Dễ |

| Khuyến nghị FPGA | Hạn chế | Nên dùng |

5. Khi nào nên dùng loại reset nào?

👉 Nên dùng reset đồng bộ khi:

-

Thiết kế FSM

-

Datapath phức tạp

-

Hệ thống có nhiều clock

-

Thiết kế chuẩn cho FPGA hiện đại

👉 Chỉ nên dùng reset không đồng bộ khi:

-

Reset nguồn (power-on reset)

-

Reset từ nút nhấn bên ngoài

-

Kết hợp với mạch đồng bộ reset release

6. Kỹ thuật chuẩn: Async assert – Sync deassert (RẤT QUAN TRỌNG)

Trong FPGA thực tế:

-

Assert reset: không đồng bộ (nhanh)

-

Deassert reset: đồng bộ theo clock

Ví dụ VHDL reset chuẩn FPGA

👉 Sau đó dùng rst_sync làm reset đồng bộ cho toàn hệ thống.

7. Reset trong FSM (ví dụ chuẩn)

✅ Dễ debug

✅ Dễ synthesize

✅ Dễ timing closure

8. Lỗi thường gặp khi xử lý reset trong VHDL

❌ Đặt reset sai sensitivity list

❌ Dùng reset không đồng bộ cho FSM lớn

❌ Nhả reset cùng lúc cho nhiều clock khác nhau

❌ Dựa vào giá trị khởi tạo (:=) thay vì reset thật