DIENTU.VN & DIENTUVIETNAM.VN Tập trung nghiên cứu và phát triển Semiconductor, từ thiết kế vi mạch đến ứng dụng thực tế.

Chuyên sâu Lập trình FPGA, triển khai thuật toán phần cứng tốc độ cao cho hệ thống nhúng và AI.

Giải pháp Camera tích hợp FPGA

Giải pháp camera tích hợp FPGA cho phép xử lý hình ảnh trực tiếp ở mức phần cứng, đáp ứng yêu cầu độ trễ thấp, tốc độ cao và độ ổn định cao so với xử lý bằng CPU/GPU truyền thống.

Hệ thống phù hợp cho các ứng dụng AI Vision, giám sát thông minh, công nghiệp, giao thông, với khả năng tùy biến pipeline xử lý ảnh, nén video và tăng tốc thuật toán theo yêu cầu thực tế.

Khi thiết kế trên FPGA (như PYNQ-Z2 / Zynq-7000), việc tối ưu LUT, Flip-Flop, BRAM và DSP là kỹ năng rất quan trọng, giúp:

-

Thiết kế fit chip

-

Tăng tốc độ (Fmax)

-

Giảm công suất

-

Dễ mở rộng về sau

Bài viết này tổng hợp nguyên tắc + mẹo thực tế đã được dùng nhiều trong dự án FPGA.

1. Hiểu rõ tài nguyên FPGA gồm những gì?

Các tài nguyên chính

-

LUT (Look-Up Table): logic tổ hợp

-

Flip-Flop (FF): lưu trạng thái

-

BRAM: bộ nhớ trong chip

-

DSP slice: nhân, MAC tốc độ cao

-

Routing: kết nối (ảnh hưởng timing)

👉 Tối ưu FPGA = dùng đúng loại tài nguyên cho đúng việc.

2. Nguyên tắc vàng #1: Giảm LUT bằng cách dùng FF và BRAM đúng chỗ

❌ Sai lầm phổ biến

-

Dùng mảng

reg [7:0] mem [0:1023]cho bộ nhớ lớn → ăn LUT -

Dùng logic để cộng/nhân số lớn → tốn LUT

✅ Cách đúng

-

Dùng BRAM cho bộ nhớ

-

Dùng DSP cho nhân/cộng lớn

Ví dụ (suy ra BRAM):

👉 Thêm attribute:

3. Nguyên tắc #2: FSM gọn – giảm số trạng thái

FSM là “kẻ ngốn tài nguyên thầm lặng” nếu viết không gọn.

Mẹo tối ưu FSM

-

Tránh FSM quá chi tiết không cần thiết

-

Gộp trạng thái có hành vi giống nhau

-

Dùng Moore FSM khi không cần phản hồi tức thì

-

Mã hóa trạng thái hợp lý

Ví dụ:

👉 FSM ít trạng thái → ít FF + LUT hơn.

4. Nguyên tắc #3: Dùng clock enable thay vì tạo clock mới

❌ Không nên

✅ Nên

Lợi ích:

-

Giảm routing clock

-

Dễ timing closure

-

Ít tài nguyên clock buffer

5. Nguyên tắc #4: Chọn độ rộng bit (bit-width) vừa đủ

❌ Lãng phí

✅ Tối ưu

👉 Mỗi bit dư = thêm FF + LUT.

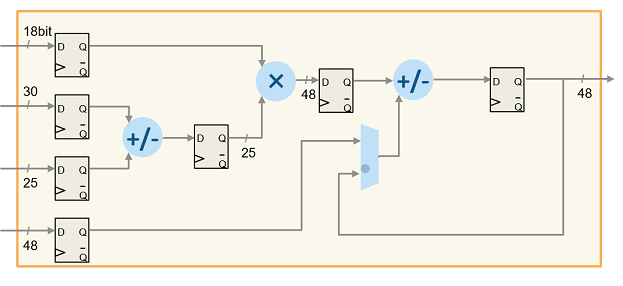

6. Nguyên tắc #5: Tận dụng DSP slice cho phép nhân/cộng

Ví dụ

-

Nếu bit-width phù hợp → tool tự suy ra DSP

-

Nếu không → nhân bằng LUT (rất tốn)

👉 Kiểm tra Synthesis Report → DSP usage.

7. Nguyên tắc #6: Pipeline để tăng Fmax (và đôi khi giảm LUT)

Pipeline giúp:

-

Giảm logic mỗi chu kỳ

-

Dễ đạt timing

-

Có thể giảm LUT do tool tối ưu tốt hơn

Ví dụ:

8. Nguyên tắc #7: Tránh logic “không dùng nhưng vẫn tồn tại”

-

Tín hiệu không dùng → vẫn có thể tốn LUT

-

Debug signal quên xóa

👉 Dùng:

-

(* keep = "false" *) -

Kiểm tra Unused logic trong report

9. Quy trình tối ưu thực tế (rất quan trọng)

-

Viết code rõ ràng, đúng chức năng

-

Run Synthesis

-

Xem:

-

LUT / FF / BRAM / DSP

-

Critical path

-

-

Tối ưu chỗ ăn tài nguyên nhất

-

Lặp lại

❗ Đừng tối ưu “mù” trước khi xem report.